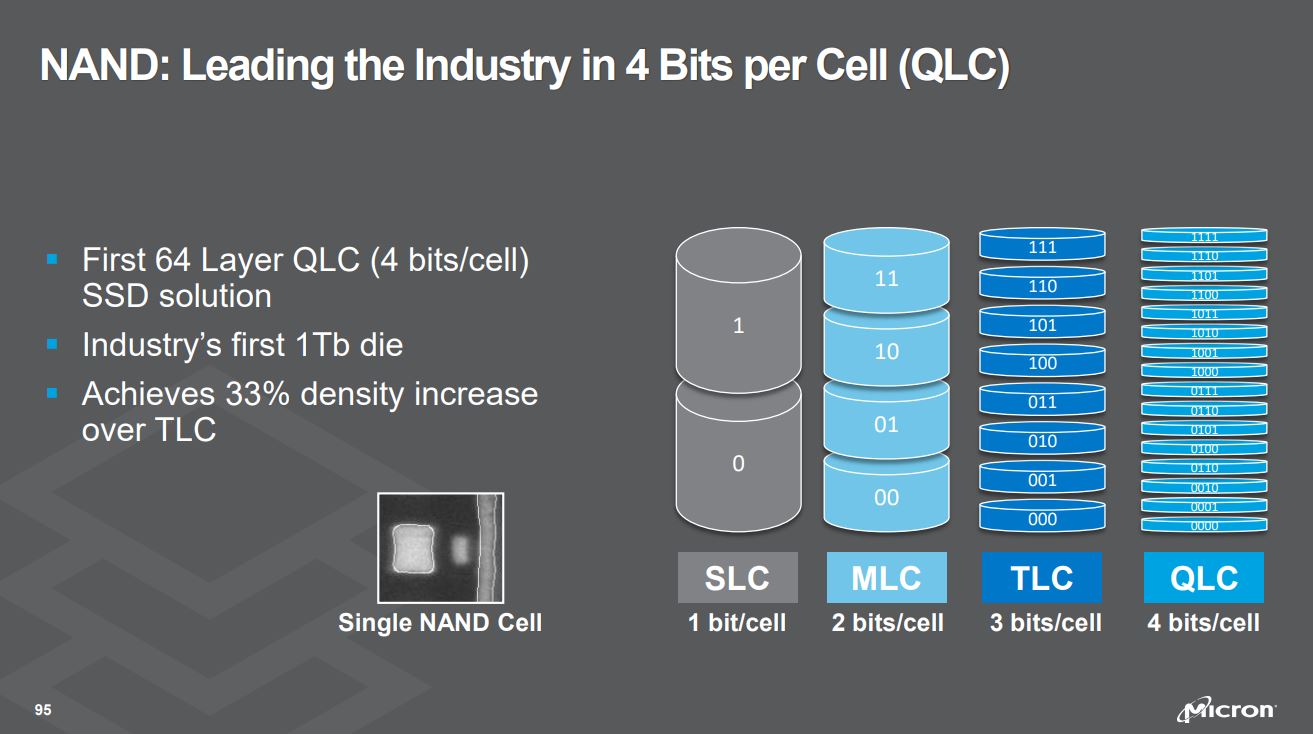

Σε συνεργασία με τη Micron Technology, η Intel ανακοίνωσε ότι είναι έτοιμη να κυκλοφορήσει το πρώτο 4bit / cell 3D NAND μνήμης.Η αύξηση της πυκνότητας επιτρέπει την ανάκτηση ενός chip ανά μνήμη και είναι σήμερα η πιο πυκνή flash μνήμη που παρήχθη ποτέ.

Η νέα QLC παρέχει 33% υψηλότερη πυκνότητα σε σύγκριση με την TLC των 3bits / cell.

Η QLC της Intel και της Micron χρησιμοποιεί 64 επίπεδα δεύτερης γενιάς 3D NAND.

Προχωρώντας, η Intel και η Micron σκοπεύουν να αυξήσουν τον αριθμό των στρώσεων στα 96 στην τρίτη γενιά μνήμης NAND, αλλά θα ακολουθήσουν την πιο κοινή τεχνολογία TLC για τις πρώτες προσπάθειες περαιτέρω κάθετης στοίβαξης. Τόσο η τεχνολογία TLC των 64 επιπέδων QLC όσο και η τεχνολογία TLC 96 επιπέδων, χρησιμοποιούν CMOS κάτω από τη συστοιχία για να διατηρούν τα μεγέθη των καλουπιών μικρά και να διατηρούν την απόδοση υπό έλεγχο.

Οι νέες μήτρες χτίζονται με τέσσερα επίπεδα αντί για την πιο κοινή κατασκευή δύο επιπέδων. Αυτό επιτρέπει μεγαλύτερο αριθμό κυψελών να διαβάζονται ή να γράφονται παράλληλα, με αποτέλεσμα μεγαλύτερο εύρος ζώνης και μεγαλύτερη συνολική απόδοση του συστήματος στο σύνολό του.

«Η κυκλοφορία του 1Tb 4bits / cell είναι ένα μεγάλο ορόσημο στην ιστορία της NVM και επιτυγχάνεται από πολυάριθμες καινοτομίες στην τεχνολογία και το σχεδιασμό που επεκτείνουν περαιτέρω την ικανότητα της τεχνολογίας Floating Gate 3D NAND», δήλωσε ο RV Giridhar, αντιπρόεδρος της Intel.

Παρόλο που οι εφαρμογές του cloud computing και τα κέντρα δεδομένων θέλουν να αποκομίσουν πρώτοι τα μέγιστα οφέλη από αυτή τη νέα τεχνολογία, θα επωφεληθούν επίσης και οι καταναλωτές. Η εξοικονόμηση κόστους από την αύξηση της πυκνότητας θα οδηγήσει, τελικά, σε δίσκους μεγαλύτερης χωρητικότητας με ελαφρώς χαμηλότερες τιμές, αν και για να βγούν στην αγορά τα προϊόντα που εκμεταλλεύονται τις νέες δυνατότητες, θα χρειαστεί χρόνος.

Πηγή : Techspot

Εμφάνιση 1-2 από 2

-

22-05-18, 23:11 QLC NAND μνήμες για την αύξηση της πυκνότητας αποθήκευσης #1

-

23-05-18, 02:56 Απάντηση: QLC NAND μνήμες για την αύξηση της πυκνότητας αποθήκευσης #2

Όπως φαίνεται ξεκάθαρα και απο το γράφημα προσθέτοντας περισσότερα bit σε κάθε cell έχεις diminishing returns (100% αύξηση χωρητικότητας απο SLC σε MLC, 50% απο MLC σε TLC κλπ) αλλά εκθετική αύξηση στις πιθανές καταστάσεις κάθε cell. Αυτό σημαίνει λιγότερο endurance, ανάγκη για ισχυρότερο error correction, μικρότερη ταχύτητα ανάγνωσης εγγραφής κλπ. Όλα αυτά σε κάποιο βαθμό μπορούν να αντιμετωπιστούν με διάφορους τρόπους (π.χ. η μετάβαση σε 3D nand αύξησε το endurance) αλλά δε νομίζω οτι θα δούμε πάνω απο 1-2 βήματα ακόμα σε αυτή τη διαδικασία. Μετά θα πρέπει να πάνε σε κάτι άλλο (MRAM, SRAM, 3dXpoint κλπ).

Παρόμοια Θέματα

-

4 χρόνια Gearbest, ειδικές τιμές για την αγορά της Ελλάδας

Από nnn στο φόρουμ Internet, web surfing και online υπηρεσίεςΜηνύματα: 0Τελευταίο Μήνυμα: 20-03-18, 11:21 -

Επτά μη δεσμευτικές προσφορές για την αγορά της Forthnet

Από nnn στο φόρουμ ΕιδήσειςΜηνύματα: 30Τελευταίο Μήνυμα: 17-03-18, 03:15 -

Εφαρμογές Smart City για την πόλη της Χαλκίδας

Από nnn στο φόρουμ ΕιδήσειςΜηνύματα: 3Τελευταίο Μήνυμα: 28-06-17, 18:45 -

Έκθεση της ΕΕΤΤ για την ανάπτυξη της ευρυζωνικότητας στην Ελλάδα το β’ εξάμηνο 2016

Από nnn στο φόρουμ ΕιδήσειςΜηνύματα: 10Τελευταίο Μήνυμα: 24-06-17, 10:07 -

Καταγγελία της Kaspersky στις Ευρωπαϊκές αρχές εναντίον της Microsoft για την πολιτική της στα προϊόντα antivirus

Από nnn στο φόρουμ ΕιδήσειςΜηνύματα: 12Τελευταίο Μήνυμα: 07-06-17, 23:44

Παράθεση

Παράθεση

Bookmarks